在當今高速發(fā)展的數(shù)字通信和電子系統(tǒng)中,時鐘信號的穩(wěn)定性與準確性至關(guān)重要。而時鐘差分Buffer作為一種關(guān)鍵的電路組件,發(fā)揮著不可或缺的作用。本文將詳細為您介紹時鐘差分Buffer的工作原理,幫助您更好地理解其在系統(tǒng)中的應(yīng)用價值。

什么是時鐘差分Buffer?

時鐘差分Buffer是一種專門用于處理差分時鐘信號的電路模塊。它接收一對具有相反相位的差分輸入信號(通常標記為A和B),經(jīng)過內(nèi)部電路的處理后,輸出同樣形式的差分信號。這種設(shè)計的主要目的是提高信號的抗干擾能力、減少電磁輻射,并確保時鐘信號在長距離傳輸或復雜電磁環(huán)境下仍能保持高質(zhì)量的特性。

工作原理詳解

差分信號的優(yōu)勢基礎(chǔ)

普通的單端時鐘信號容易受到外界噪聲的影響,因為其參考電平通常是地,而實際環(huán)境中存在各種干擾源會耦合到地線上,進而影響信號的質(zhì)量。與之相比,差分信號采用兩根線傳輸互為相反相位的信號,接收端通過比較這兩個信號的差異來恢復原始信息。由于干擾往往同時作用于兩根線上,在相減的過程中會被大大削弱甚至消除,從而顯著提高了信號的信噪比和抗干擾能力。時鐘差分Buffer正是基于這一原理構(gòu)建的。

輸入級:精準采集與初步整理

當差分時鐘信號輸入到Buffer時,首先進入的是輸入級電路。這一部分通常由高速、高帶寬的差分對管組成,如雙極型晶體管或場效應(yīng)管構(gòu)成的共射極/共源極放大器。它們能夠迅速地響應(yīng)輸入信號的變化,將微弱的差分電壓轉(zhuǎn)換為相應(yīng)的電流變化。同時,輸入級還具備一定的增益調(diào)節(jié)功能,可以根據(jù)后續(xù)階段的需要進行適當?shù)姆糯蠡蛩p,以保證整個信號鏈路的平衡與穩(wěn)定。例如,在一些高精度的應(yīng)用中,輸入級可能會采用帶有自動增益控制的電路,動態(tài)地調(diào)整增益系數(shù),補償因溫度變化、器件老化等因素引起的信號幅度波動。

中間級:信號整形與隔離強化

經(jīng)過輸入級的初步處理后,信號進入中間級。中間級的主要任務(wù)是對信號進行進一步的整形和隔離。一方面,它會使用限幅器等元件將信號限制在一個特定的電壓范圍內(nèi),防止過沖和下沖現(xiàn)象的發(fā)生,使信號的邊緣更加陡峭,有利于提高時序的準確性。另一方面,通過光耦、變壓器等隔離器件實現(xiàn)電氣上的隔離,阻斷不同部分之間的直流通路,避免共模干擾的傳播。這在多電源域、遠距離傳輸?shù)葓鼍爸杏葹橹匾梢杂行Х乐沟丨h(huán)路等問題導致的系統(tǒng)故障。比如在一個大型數(shù)據(jù)中心的網(wǎng)絡(luò)設(shè)備中,不同機架之間存在較大的電位差,此時時鐘差分Buffer中的隔離措施就能確保時鐘信號不受這些電位差的影響,穩(wěn)定地傳輸。

輸出級:驅(qū)動與適配優(yōu)化

最后的輸出級負責將處理好的信號以足夠的強度驅(qū)動負載。為了適應(yīng)不同的負載特性(如容性負載、感性負載等),輸出級一般采用推挽式結(jié)構(gòu)或其他合適的驅(qū)動方式,提供較大的輸出電流能力。并且,輸出級的阻抗匹配設(shè)計也非常關(guān)鍵,它能使信號在傳輸線上的反射最小化,保證信號完整性。在一些高速數(shù)據(jù)傳輸系統(tǒng)中,如果輸出阻抗不匹配,就會引起信號反射,導致誤碼率上升。時鐘差分Buffer通過精心調(diào)整輸出級的參數(shù),確保與連接的傳輸線和接收設(shè)備的輸入阻抗良好匹配,實現(xiàn)高效、可靠的信號傳輸。

應(yīng)用場景及意義

時鐘差分Buffer廣泛應(yīng)用于眾多領(lǐng)域。在計算機主板上,它用于CPU與其他芯片組之間的時鐘同步,保證各個部件協(xié)調(diào)工作;在通信基站中,作為射頻模塊的時鐘源,為海量數(shù)據(jù)的收發(fā)提供精準定時;在工業(yè)自動化控制系統(tǒng)里,確保各個控制器和執(zhí)行器按照準確的節(jié)拍運行。其重要性體現(xiàn)在以下幾個方面:一是提高系統(tǒng)的可靠性,通過增強抗干擾能力和信號完整性,降低系統(tǒng)出錯的概率;二是實現(xiàn)長距離傳輸,借助差分結(jié)構(gòu)和隔離技術(shù),突破單端信號傳輸?shù)木嚯x限制;三是便于系統(tǒng)集成,標準化的接口和良好的電氣性能使其能夠方便地與其他模塊連接。

總之,時鐘差分Buffer以其獨特的工作原理和卓越的性能,成為現(xiàn)代電子系統(tǒng)中不可或缺的一部分。深入了解它的工作機制,有助于我們在設(shè)計和調(diào)試電路時更好地運用這一技術(shù),提升系統(tǒng)的整體性能。無論是從事硬件開發(fā)的工程師還是相關(guān)領(lǐng)域的研究人員,都有必要掌握時鐘差分Buffer的知識,以便在實際項目中做出更明智的選擇和優(yōu)化。

時鐘系統(tǒng)

時鐘系統(tǒng)

芯片

芯片

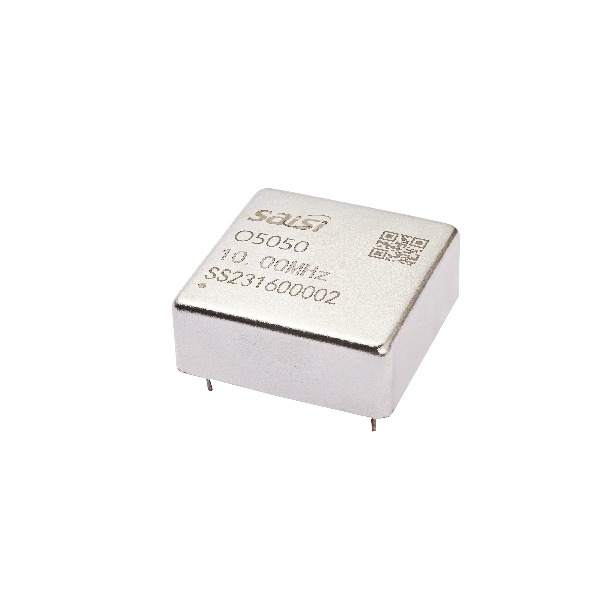

晶振&原子鐘

晶振&原子鐘

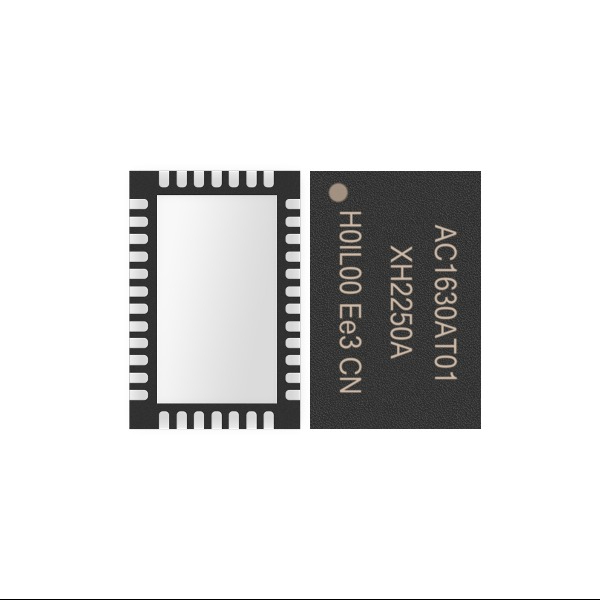

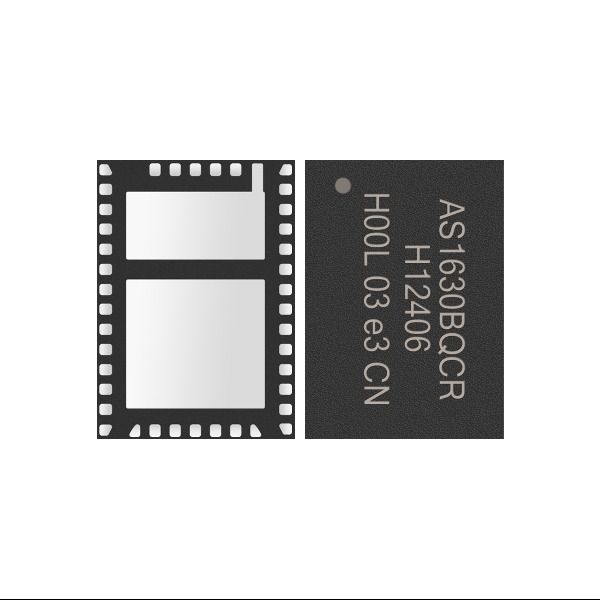

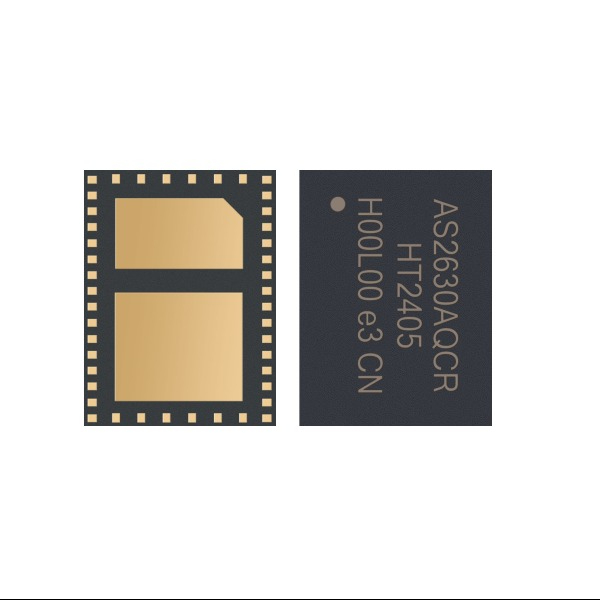

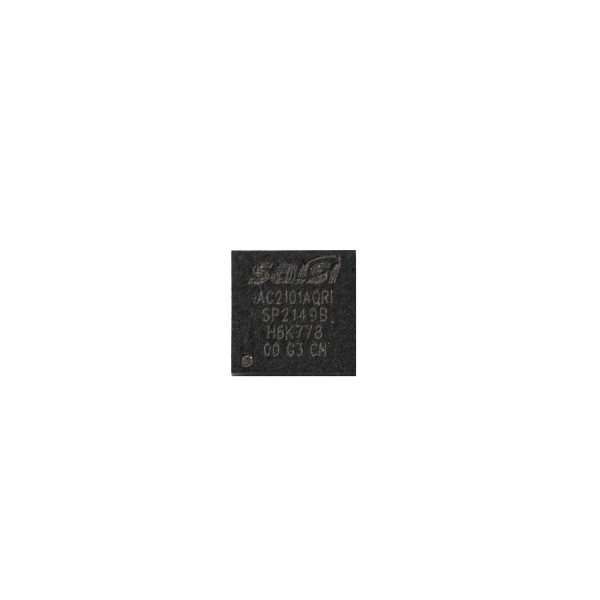

授時板卡

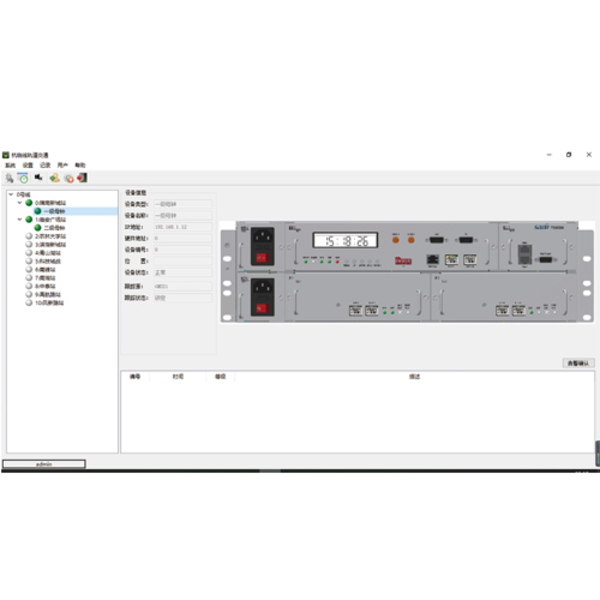

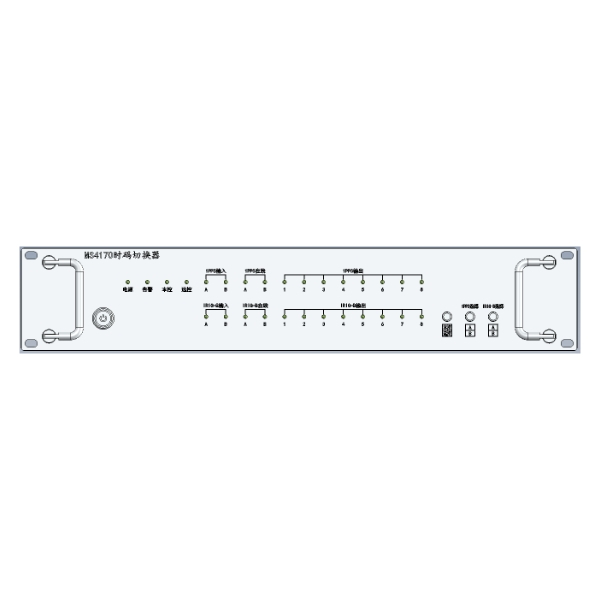

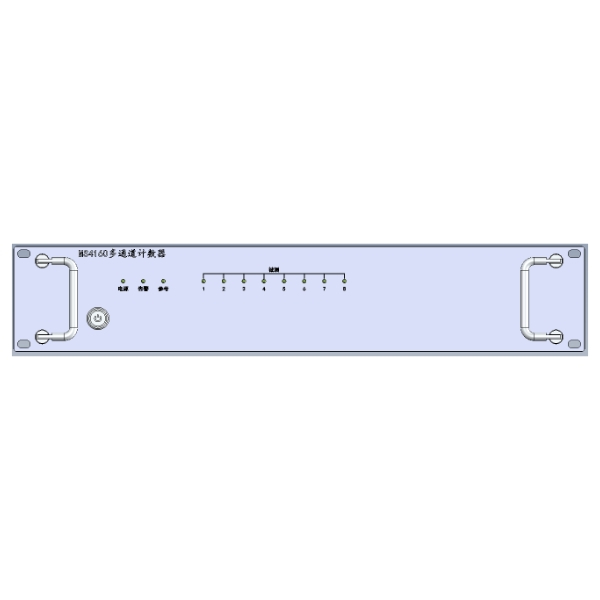

NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

授時板卡

NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

人才研學中心

人才研學中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思